I possess a wire vector with 64 parts;

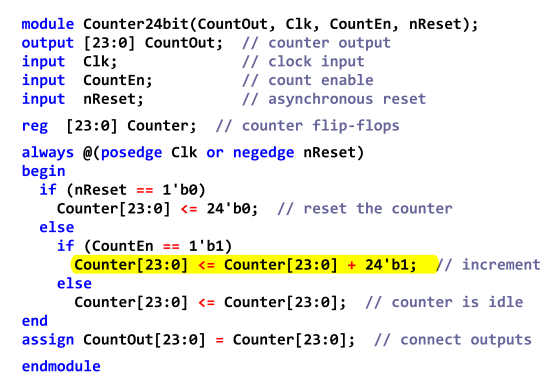

Verilog code for a 4-bit unsigned up counter with a synchronous load with a constant. Verilog - 13 Restricted FSM Implementation Style ˙ '!! ˙˝% )7 ˙˝% i% ˙ ˙˝ ˙ r ˙!

I would like to calculate the sum of these bits or, equivalently, count the quantity of types.

What is usually the greatest method to perform this? (it should end up being synthesizable)

Gap Star

Gap SuperstarGap Superstar

1,3563 magic badges21 metallic badges49 bronze badges

3 Answers

I prefer using for-loops as they are less complicated to range and need less writing (and therefore less susceptible to typos).

SystemVerilog (IEEE Std 1800):

Verilog (IEEE Std 1364-2005):

GregGreg13.7k5 silver badges37 silver precious metal badges54 bronze badges

'Best' is rather subjective, but a easy and obvious formula would just become:

You might become capable to believe tough and arrive up with something that produces better synthesized results, but this is possibly a great begin until a timing tool says it't not good enough.

Jared DavisJared Davis

The following solution utilizes a function to determine the total quantity of collection (to High) bits in a 64-bits wide coach:

consumer11034079user11034079